1. Introducción

Los osciladores de cuarzo generan señales de reloj altamente estables que son necesarias en casi todos los sistemas electrónicos, desde circuitos simples de microcontroladores hasta sistemas de transmisión de datos de alta velocidad.

La señal de salida de un oscilador debe ser compatible con la familia lógica o interfaz posterior. A lo largo de las décadas se han desarrollado diversos estándares de salida, cada uno adaptado a los requisitos de su época y aplicación.

Este documento proporciona una descripción general completa de los siete tipos de señales de salida más comunes en osciladores de cuarzo: CMOS, TTL, onda sinusoidal recortada, sinusoidal, LVPECL, LVDS y HCSL.

Para cada tipo se describen el desarrollo histórico, las características eléctricas, la forma de onda típica y las áreas de aplicación preferidas.

2. Desarrollo histórico

El desarrollo de los tipos de señales de salida está estrechamente vinculado con la evolución de la tecnología de semiconductores y las crecientes exigencias en frecuencias de reloj e integridad de la señal:

2.1 TTL (Lógica Transistor-Transistor) – desde aprox. 1964

TTL fue uno de los primeros estándares de lógica digital ampliamente difundidos y fue introducido por Texas Instruments como la serie 7400. Los osciladores con salida TTL funcionan con una tensión de alimentación de 5 V y proporcionan rangos de nivel directamente compatibles con puertas TTL. El estándar configuró la electrónica digital durante décadas y fue el estándar lógico dominante hasta los años 90.

2.2 CMOS (Complementary Metal-Oxide-Semiconductor) – desde aprox. 1968

La tecnología CMOS fue desarrollada originalmente por RCA y se caracteriza por un consumo de corriente en reposo extremadamente bajo. Los osciladores CMOS proporcionan señales de salida riel a riel, lo que significa que la salida oscila casi exclusivamente entre 0 V y VCC. Con la continua miniaturización y la tendencia hacia voltajes de alimentación más bajos (3,3 V, 2,5 V, 1,8 V), CMOS se ha convertido en el estándar de salida más utilizado para osciladores CMOS.

2.3 Sinus – desde los inicios de la técnica de osciladores

Las señales de salida sinusoidales son tan antiguas como la propia tecnología de osciladores. Los osciladores sinusoidales oscilan físicamente sinusoidalmente; todas las demás formas de señal son generadas por circuitos posteriores. Las salidas sinusoidales se prefieren en tecnología de alta frecuencia, instrumentos de medición y procesamiento de señales analógicas porque no generan armónicos.

2.4 Clipped Sine Wave – desde aprox. años 70

La salida Clipped Sine Wave representa un compromiso entre la salida sinusoidal y la de onda cuadrada. La señal sinusoidal se recorta en los picos, creando flancos más pronunciados que con el seno puro pero menos armónicos que con una señal de onda cuadrada. Este tipo de salida se utilizó especialmente en telecomunicaciones y en aplicaciones de alta frecuencia antiguas. Los circuitos Clipped Sine Wave se utilizan hoy principalmente en TCXOs. Con esta tecnología se pueden construir TCXOs significativamente más eficientes energéticamente que con tecnología CMOS. Los CSW-TCXO se utilizan por ello como referencia en dispositivos de navegación, sistemas de llamada de emergencia y pasarelas. En todas partes donde se necesita alcance de señal (radio) y un posicionamiento de alta precisión.

2.5 LVPECL (Low-Voltage Positive Emitter-Coupled Logic) – desde aprox. años 90

Con la necesidad de frecuencias de reloj cada vez más altas en sistemas de red y telecomunicaciones, surgió LVPECL como lógica de salida diferencial rápida. LVPECL se basa en la técnica clásica ECL (Emitter-Coupled Logic), desarrollada ya en los años 60 para aplicaciones de alta velocidad, y la adapta para tensiones de alimentación más bajas (3,3 V en lugar de -5,2 V). LVPECL ofrece tiempos de conmutación extremadamente cortos y es adecuado para frecuencias muy superiores a 1 GHz.

2.6 LVDS (Low-Voltage Differential Signaling) – desde 1994

LVDS fue introducido en 1994 como estándar ANSI/TIA/EIA-644 y optimiza la transmisión diferencial de señal para bajo consumo y altas velocidades de datos. La pequeña excursión de tensión diferencial de solo 350 mV permite conmutaciones rápidas con emisión electromagnética mínima. LVDS está hoy ampliamente difundido en interfaces de pantalla, enlaces de datos serie y clocking FPGA.

2.7 HCSL (High-Speed Current Steering Logic) – desde aprox. 2002

HCSL fue desarrollado específicamente para el estándar PCI Express y es el estándar de reloj de referencia desde la primera generación PCIe. El PCI-SIG especificó HCSL como una señal diferencial basada en modo de corriente con excursión de tensión muy baja, optimizada para los relojes de referencia de 100 MHz en sistemas PCIe. HCSL es hoy indispensable en cada PC, servidor y sistema embebido con interfaz PCIe.

3. Visión general de las formas de onda

Los siguientes diagramas muestran las formas de onda idealizadas de los siete tipos de salida. Observe los diferentes rangos de tensión y excursiones – estos son determinantes para la compatibilidad con los receptores posteriores.

3.1 CMOS

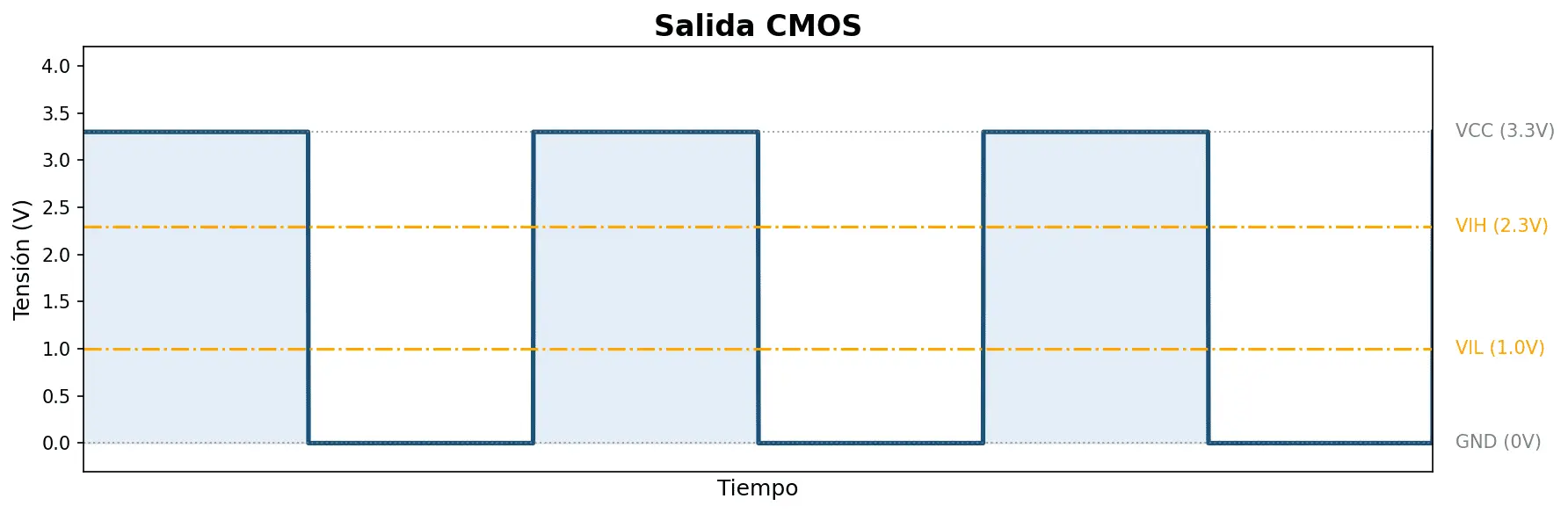

Fig. 1: Señal de salida CMOS – onda cuadrada rail-to-rail entre 0 V y VCC (aquí 3,3 V)

La señal CMOS se caracteriza por su excursión de tensión completa entre GND y VCC. Los umbrales de entrada VIL y VIH se sitúan típicamente en el 30 % y 70 % de VCC respectivamente, lo que garantiza un amplio margen de ruido. Las estructuras de driver de salida simétricas (MOSFET de canal P/canal N) permiten tiempos de subida y bajada prácticamente iguales.

3.2 TTL

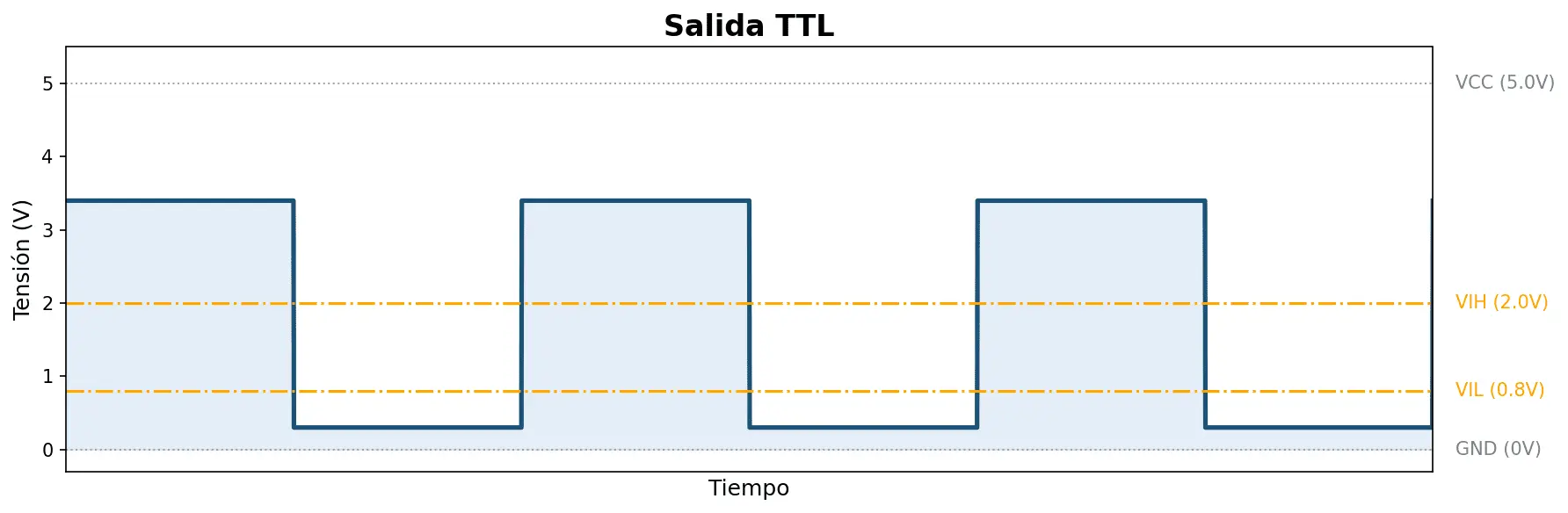

Fig. 2: Señal de salida TTL – VOH típicamente 3,4 V, VOL típicamente 0,3 V a 5 V de alimentación

A diferencia de la salida CMOS, TTL no alcanza niveles rail-to-rail. El nivel alto (VOH) se sitúa típicamente en 3,4 V (mínimo 2,4 V), el nivel bajo (VOL) en un máximo de 0,4 V. Los umbrales asimétricos (VIL = 0,8 V, VIH = 2,0 V) se derivan de la arquitectura de transistores bipolares. La denominada «zona prohibida“ entre 0,8 V y 2,0 V no debe adoptarse en funcionamiento estático.

3.3 Clipped Sine Wave

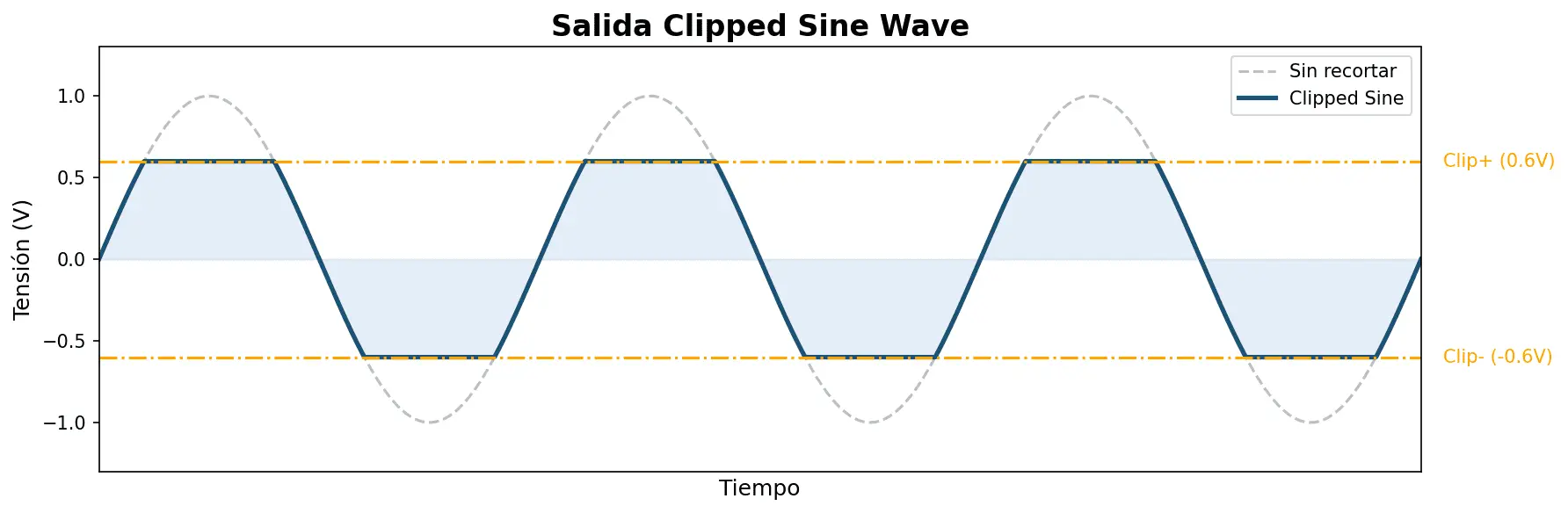

Fig. 3: Salida Clipped Sine Wave – señal sinusoidal con picos de amplitud recortados

En la salida Clipped Sine Wave, la señal sinusoidal natural del resonador de cuarzo se recorta en umbrales definidos. La línea discontinua muestra la forma sinusoidal sin recortar. El clipping crea cruces por cero más pronunciados que con el seno puro, facilitando el control de la lógica posterior, mientras que el contenido armónico se mantiene moderado.

3.4 Sinus

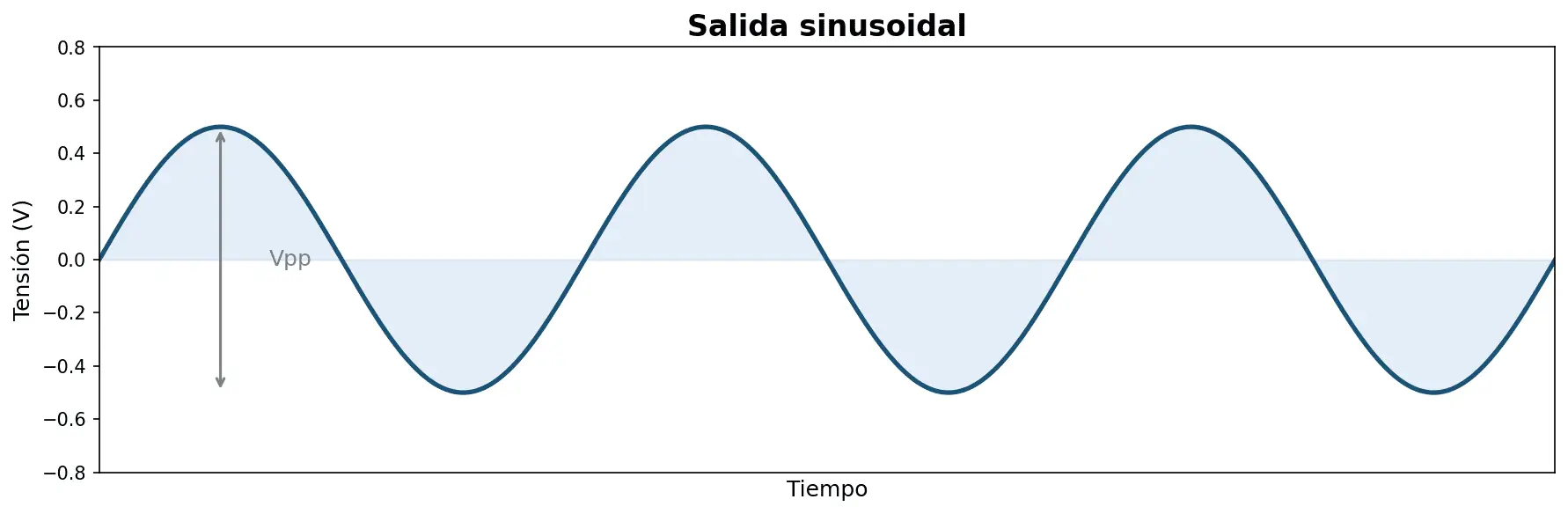

Fig. 4: Salida sinusoidal – señal sinusoidal pura con tensión pico a pico definida (Vpp)

La salida sinusoidal proporciona el espectro más limpio de todas las formas de salida: idealmente una sola línea espectral a la frecuencia fundamental. La amplitud se especifica como tensión pico a pico (Vpp) o como potencia en dBm. Los valores típicos son de 0,5 a 1,0 Vpp o de 0 a +13 dBm en sistemas de 50 Ω.

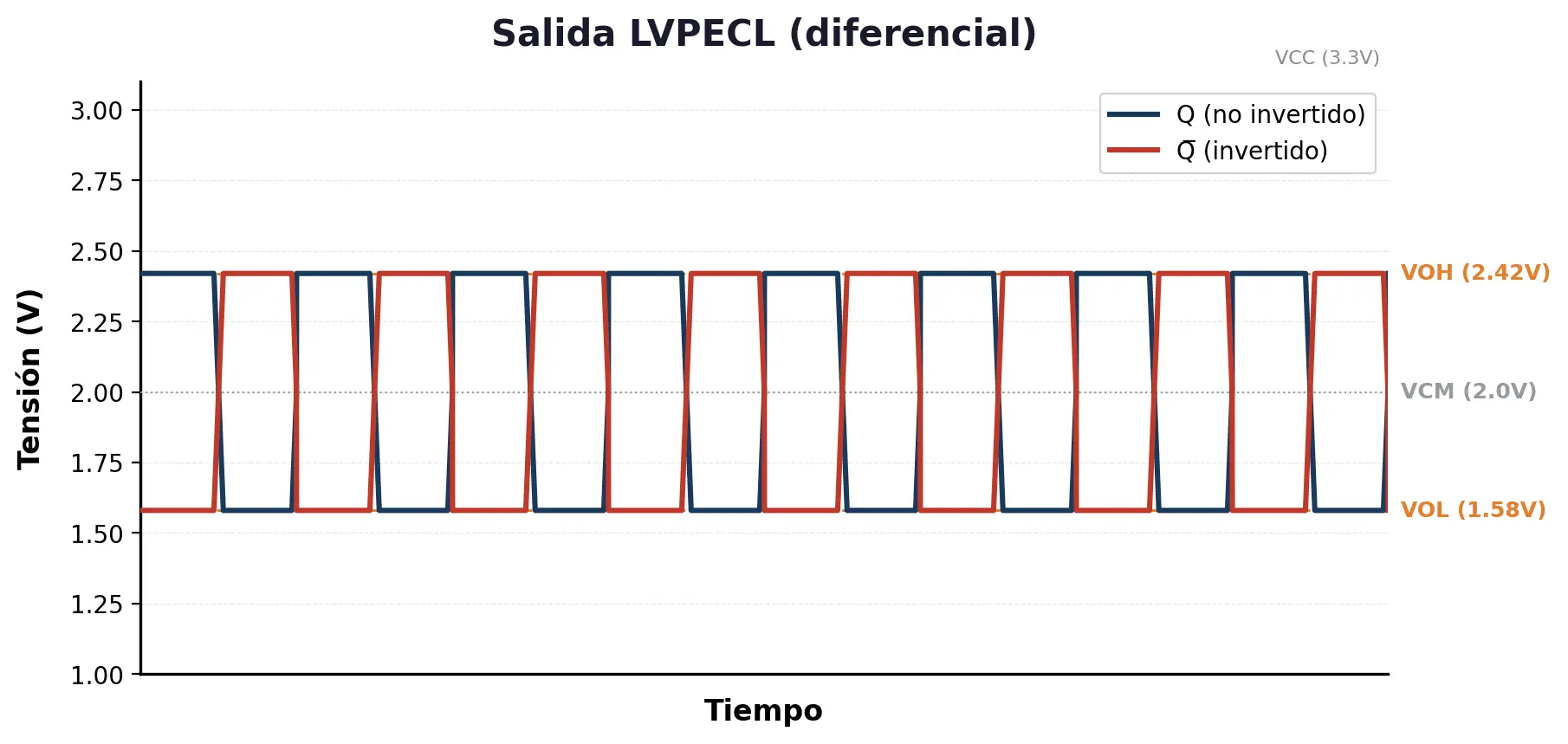

3.5 LVPECL

Fig. 5: Salida LVPECL – señal diferencial con aprox. 800 mV de excursión total en torno a VCC–1,3 V

LVPECL utiliza conducción de señal diferencial: dos salidas complementarias (Q y Q̅) conmutan en contrafase alrededor de un nivel de modo común (VCM), típicamente en VCC–1,3 V. La excursión de tensión diferencial es de aprox. 800 mV. La arquitectura de fuente de corriente permite tiempos de conmutación extremadamente rápidos con mínima tendencia al overshoot.

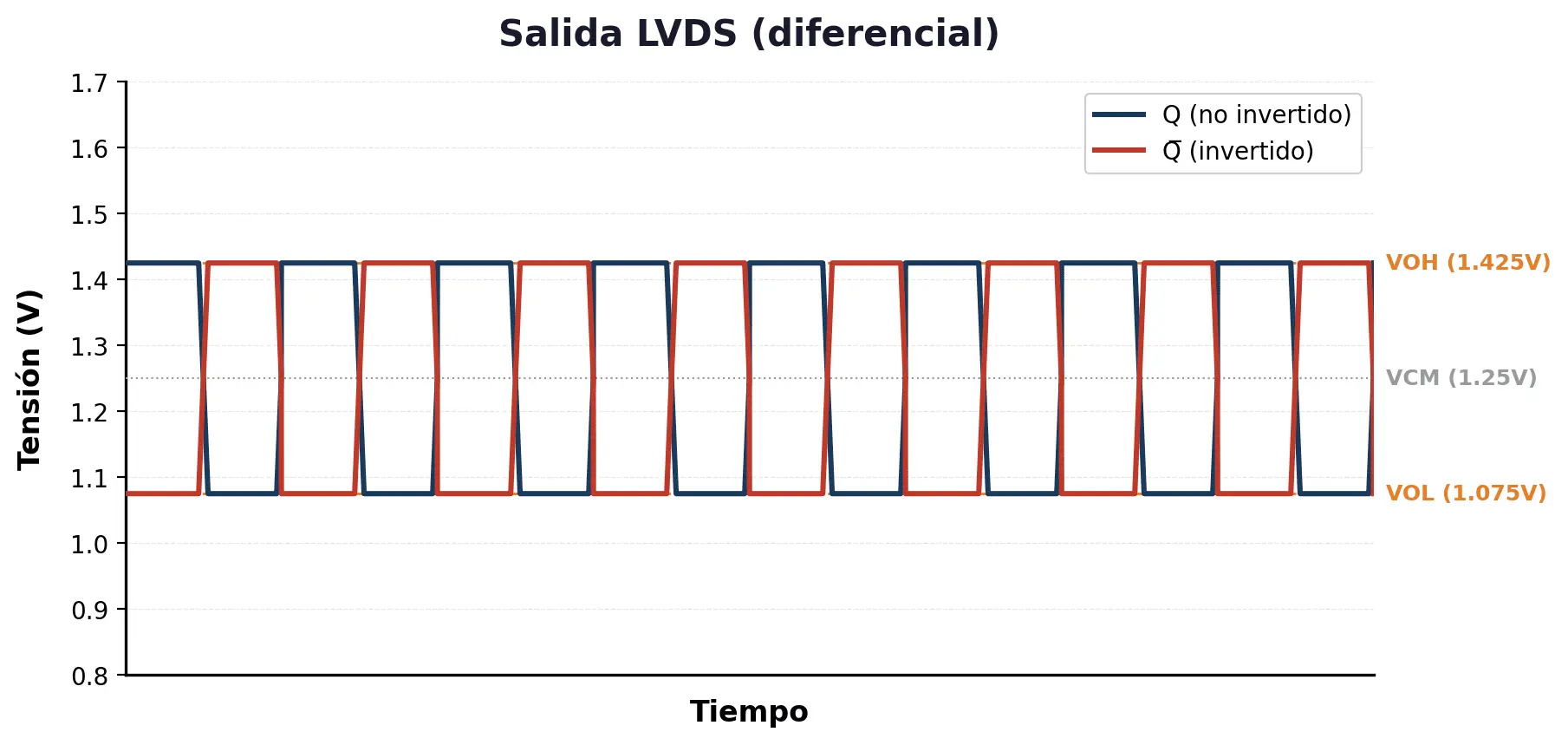

3.6 LVDS

Fig. 6: Salida LVDS – señal diferencial con solo 350 mV de excursión en torno a 1,25 V de nivel de modo común

LVDS se caracteriza por su excursión de tensión diferencial particularmente baja de solo 350 mV. El nivel de modo común se sitúa en 1,25 V. Gracias al driver controlado por corriente (típicamente 3,5 mA) y la terminación de 100 Ω, se logra una alta integridad de señal con consumo mínimo. La baja amplitud minimiza la emisión electromagnética.

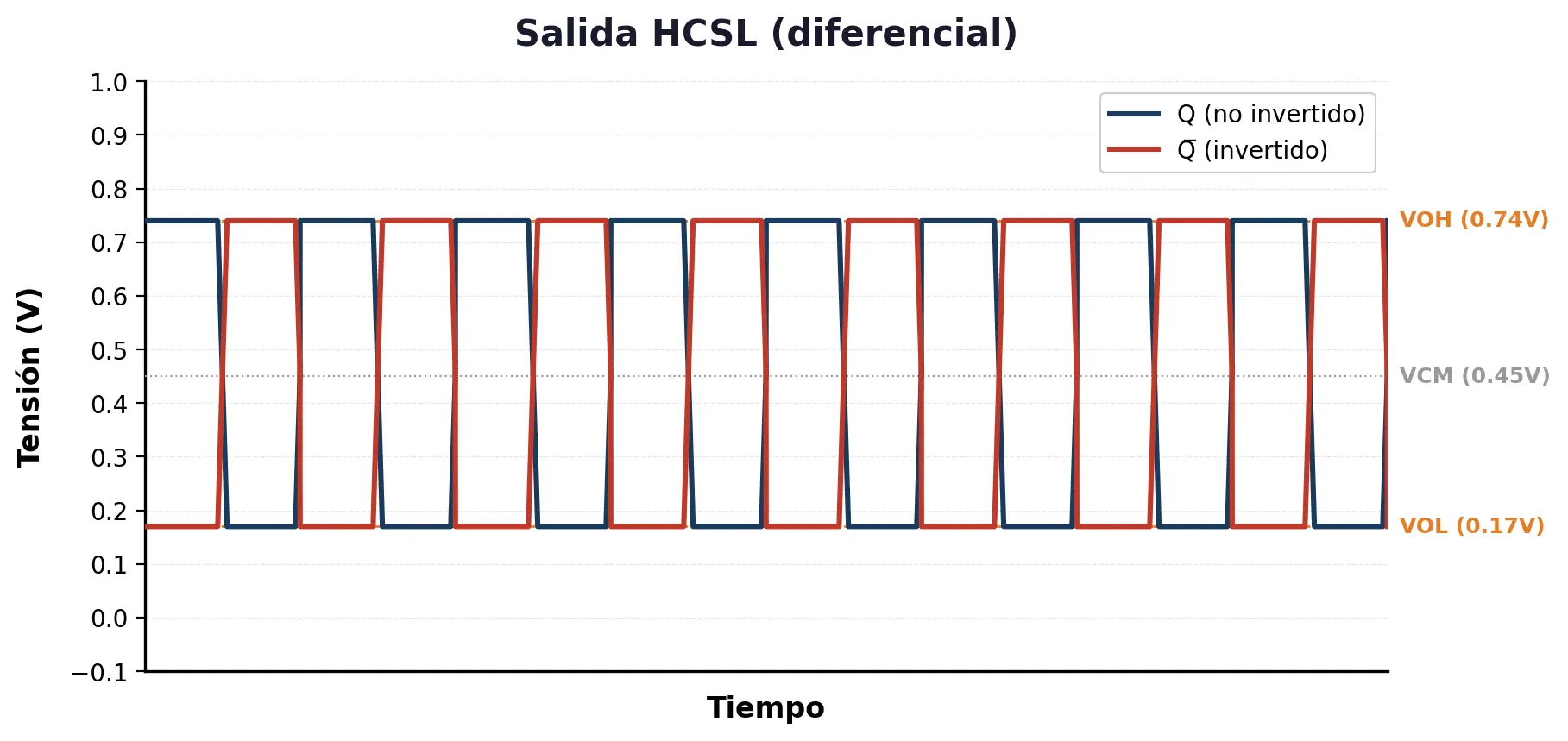

3.7 HCSL

Fig. 7: Salida HCSL – señal diferencial basada en modo de corriente para relojes de referencia PCIe

HCSL opera con una excursión de tensión muy baja: VOH se sitúa típicamente en 0,74 V y VOL en 0,17 V, resultando en un nivel de modo común de aprox. 0,45 V. La arquitectura de control de corriente está específicamente optimizada para los requisitos de la especificación PCIe y permite una adaptación de impedancia precisa mediante terminaciones de 50 Ω a masa.

4. comparación de las señales de salida

La siguiente tabla resume las propiedades esenciales de los siete tipos de salida:

Tipo | Tipo de señal | VCC (V) | VOH/ VOL (V) | Diff. desviación | Frecuencia máx. aprox. | Aplicación típica |

| CMOS | Single-ended | 1,8-5,0 | VCC/ 0 | - | ~285 MHz | Microcontroladores, FPGAs, técnica digital general |

| TTL | Single-ended | 1,8-5,0 | 3,4/ 0,3 | - | ~150 MHz | Sistemas legacy, controles industriales |

| Clipped Sine | Un solo extremo | 1,8/2,5/3,3 | variable | - | ~200 MHz | Telecomunicaciones, aplicaciones RF |

| Sinus | Un solo extremo | 3,3/5,0/12 | variable | - | >1 GHz | Técnica RF, instrumentos de medición, síntesis de frecuencia |

| LVPECL | Diferencial | 2,5/3,3 | ~2,4/ ~1,6 | ~800 mV | >3 GHz | Equipos de red, SONET/SDH, clocking de alta velocidad |

| LVDS | Diferencial | 2,5/3,3 | ~1,43/ ~1,07 | 350 mV | >1 GHz | Interfaces de pantalla, enlaces serie, clocking FPGA |

| HSL | Diferencial | 3,3 | 0,74/ 0,17 | ~570 mV | ~200 MHz | Reloj de referencia PCI Express (100 MHz) |

5. Diferencias esenciales en detalle

5.1 Single-Ended vs. diferencial

La diferencia más fundamental entre los tipos de salida es la conducción de la señal. CMOS, TTL, Clipped Sine Wave y Sinus son señales single-ended – se referencian a una masa común. LVPECL, LVDS y HCSL, en cambio, son señales diferenciales con dos líneas complementarias. Las señales diferenciales ofrecen ventajas decisivas a frecuencias más altas: suprimen las perturbaciones de modo común, permiten excursiones de tensión más pequeñas y, por tanto, tiempos de conmutación más rápidos con menor emisión electromagnética.

5.2 Excursión de tensión y margen de ruido

CMOS ofrece con su salida rail-to-rail la mayor excursión de tensión absoluta y, por tanto, el mejor margen de ruido estático. TTL tiene un margen de ruido más limitado debido a sus niveles asimétricos. Los estándares diferenciales (LVPECL, LVDS, HCSL) compensan sus menores excursiones de tensión mediante el rechazo de modo común de la transmisión diferencial, lo que les permite funcionar de forma más fiable en entornos con perturbaciones que las señales single-ended.

5.3 Consumo de corriente

Los osciladores CMOS consumen prácticamente cero corriente en estado estático; el consumo aumenta proporcionalmente con la frecuencia (potencia dinámica disipada). TTL tiene un consumo de corriente en reposo constantemente más alto debido a la arquitectura bipolar. LVPECL requiere resistencias de terminación externas y tiene el mayor consumo de corriente de los estándares diferenciales. LVDS es conocido por su bajo consumo (típicamente 3,5 mA de corriente de driver). HCSL se sitúa en términos de consumo entre LVDS y LVPECL.

5.4 Rango de frecuencia y áreas de aplicación principales

Para frecuencias de hasta aproximadamente 200 MHz, los osciladores CMOS son la primera opción en la mayoría de los casos debido a su versatilidad, diseño de circuito simple y amplia disponibilidad. Por encima de aproximadamente 200 MHz, se recomiendan salidas diferenciales. LVPECL ofrece las frecuencias más altas (>3 GHz) y se utiliza en equipos de redes y telecomunicaciones. LVDS cubre un amplio rango medio y es particularmente común en aplicaciones de FPGA y pantallas. HCSL está optimizado para su caso de uso específico: el reloj de referencia de 100 MHz para PCI Express.

5.5 Terminación y complejidad del circuito

Las salidas CMOS y TTL generalmente no requieren terminación externa para longitudes de pista cortas – esto las hace especialmente sencillas en su uso. LVPECL requiere obligatoriamente resistencias de terminación externas (típicamente: terminación Thévenin hacia VCC–2 V o resistencias a masa), lo que aumenta la complejidad del circuito. LVDS se termina por defecto con una resistencia diferencial de 100 Ω en el receptor. HCSL utiliza resistencias de 50 Ω a masa en cada salida.

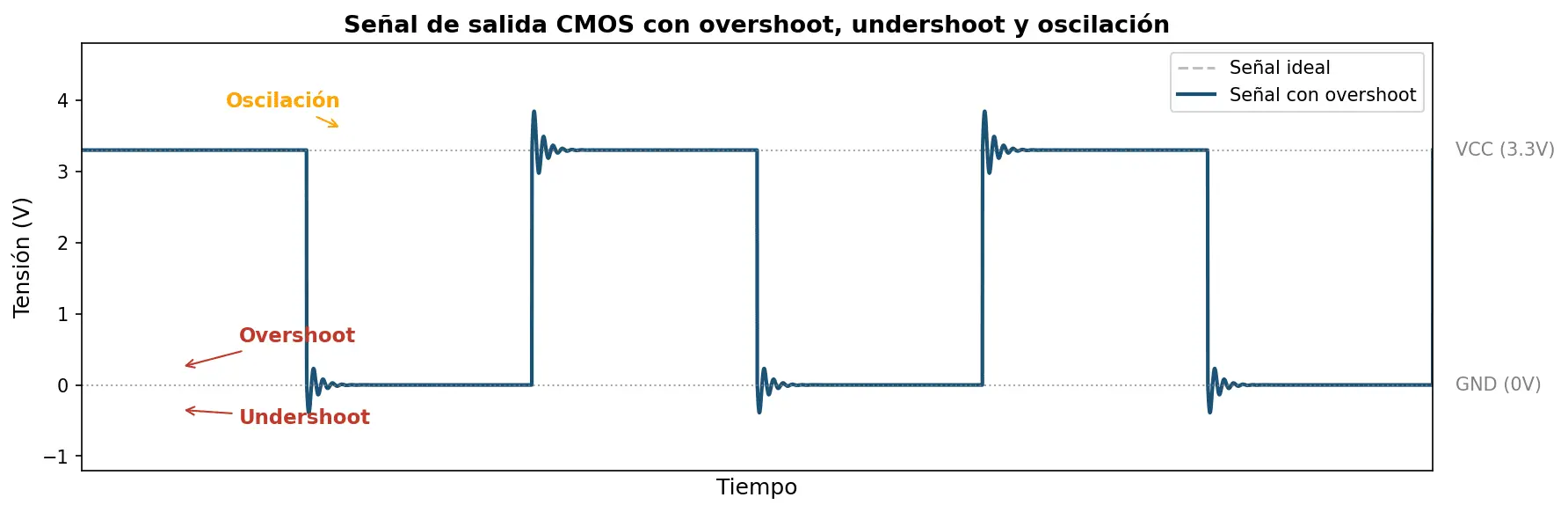

6. Overshoot en las señales de salida de osciladores

6.1 Qué es el overshoot?

El sobreimpulso y el subimpulso son breves picos de tensión que se producen durante operaciones de conmutación rápida. En un flanco ascendente, la tensión supera brevemente VCC (sobreimpulso), mientras que en un flanco descendente, cae ligeramente por debajo de GND (subimpulso). Estos picos suelen ir seguidos de oscilaciones amortiguadas conocidas como "resonancia".

La causa reside en la combinación de los flancos de conmutación muy pronunciados del driver de salida y las inductancias y capacitancias parásitas de la pista, el encapsulado y la capacidad de carga. Físicamente se forma un circuito resonante a partir de la inductancia de la línea y la capacitancia de entrada del receptor. Cuanto más pronunciado es el flanco y más larga la pista, más marcado es el overshoot.

Fig. 8: Señal de salida CMOS con overshoot – Overshoot por encima de VCC, undershoot por debajo de GND y ringing posterior

6.2 Por qué es problemático el overshoot?

Los overshoots que superan VCC o caen por debajo de GND pueden polarizar en conducción directa los diodos de protección ESD del circuito receptor, generando corrientes parásitas. En el peor de los casos, esto puede provocar un latch-up – un flujo de corriente descontrolado a través de estructuras tiristoras parásitas en el circuito CMOS, que puede destruir el componente. Un fuerte ringing puede además causar múltiples disparos en las entradas de reloj cuando la tensión cruza el umbral de conmutación varias veces, provocando un comportamiento erróneo del sistema.

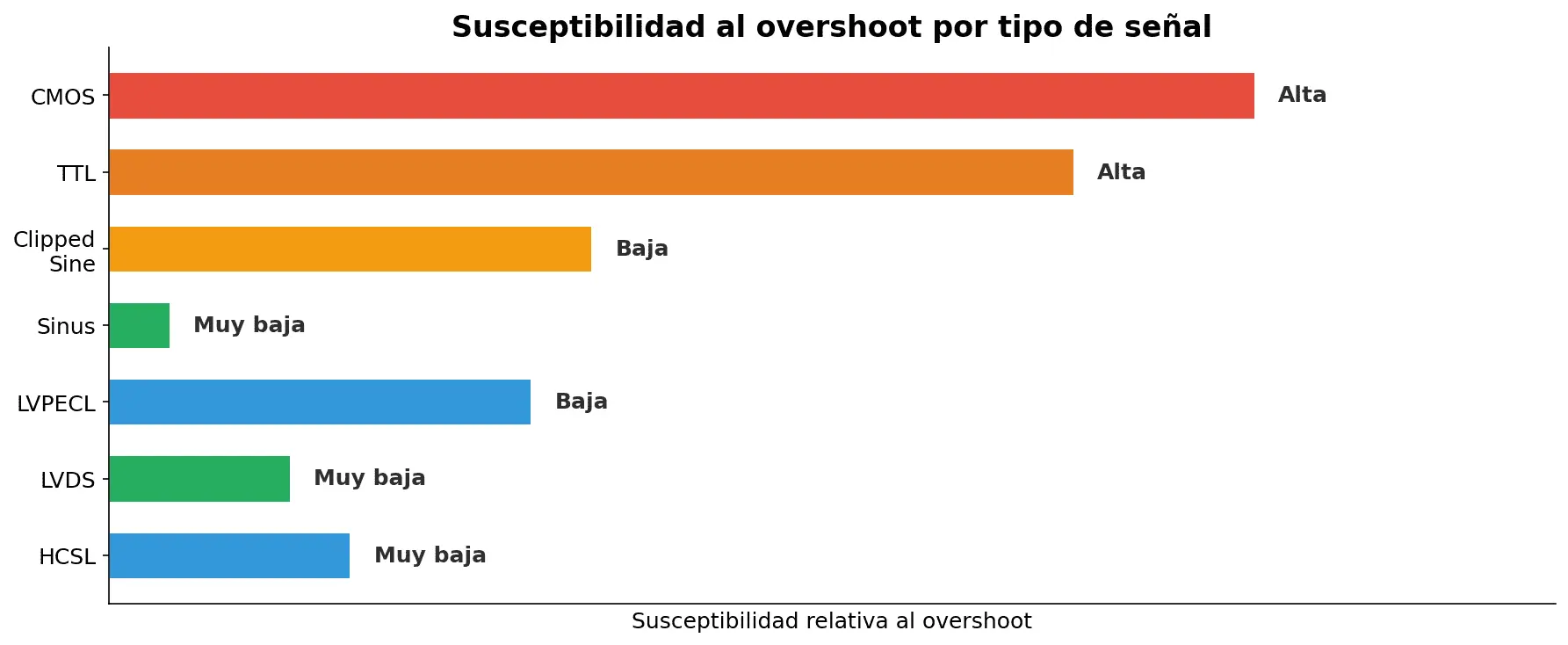

6.3 Comparación: overshoot por tipo de señal

La susceptibilidad al overshoot difiere considerablemente entre los diferentes tipos de salida. El siguiente gráfico muestra la susceptibilidad relativa en comparación:

6.4 Overshoot en señales single-ended

CMOS: El más afectado. Los drivers MOSFET simétricos de canal P/N generan flancos muy pronunciados que, combinados con las inductancias de pista, causan overshoots marcados. Especialmente con los osciladores CMOS modernos de baja tensión (1,8 V), los overshoots pueden ser significativos en relación con la tensión de alimentación.

TTL: También susceptible, aunque por razones ligeramente diferentes. La etapa de salida asimétrica totem-pole genera un breve pico de corriente en el flanco de subida cuando ambos transistores conducen simultáneamente (cross-conduction). Los flancos típicamente algo más lentos en comparación con CMOS moderno atenúan ligeramente el problema.

Clipped Sine Wave: Significativamente menos susceptible. Los picos de amplitud limitados y los flancos comparativamente suaves producen mucha menos energía de alta frecuencia que pueda excitar reflexiones y ringing. El clipping actúa como un limitador de amplitud natural que suprime el overshoot ya en la señal.

Onda sinusoidal: Prácticamente inmune a la sobreoscilación clásica. Dado que la señal no presenta transiciones de flanco abruptas, no se generan pulsos de energía de banda ancha que puedan excitar resonancias de línea. Sin embargo, los desajustes de impedancia pueden generar ondas estacionarias y reflexiones que alteran la amplitud de la señal en ciertos puntos. Esto se controla mediante la terminación de RF clásica (terminación de 50 Ω o 75 Ω).

6.5 Overshoot en señales diferenciales

LVPECL: Intrínsecamente bien suprimido gracias a la etapa de salida de fuente de corriente. El control de corriente limita naturalmente la pendiente máxima de los flancos. Con una terminación insuficiente pueden producirse reflexiones, ya que LVPECL opera a frecuencias muy altas. El circuito Thévenin o seguidor de emisor correcto es aquí decisivo – no principalmente por el overshoot, sino para asegurar el punto de trabajo correcto y evitar reflexiones.

LVDS: Muy robusto por diseño. El driver controlado por corriente suministra una corriente constante de típicamente 3,5 mA a la terminación diferencial de 100 Ω, lo que limita físicamente la excursión de tensión. Incluso con discontinuidades de impedancia, las reflexiones permanecen pequeñas ya que la baja excursión de tensión de solo 350 mV proporciona poca energía para perturbaciones. LVDS es uno de los estándares más tolerantes en cuanto a integridad de señal.

HCSL: Se comporta de manera similar a LVDS gracias a la arquitectura basada en corriente. La excursión de tensión muy baja y la terminación de 50 Ω a masa aseguran una adaptación de impedancia limpia. En la especificación PCIe, el overshoot admisible está explícitamente definido y estrechamente tolerado, de modo que los osciladores conformes con HCSL cumplen intrínsecamente estos requisitos.

6.6 Contramedidas para el control del overshoot

La medida más eficaz para señales single-ended (en particular CMOS y TTL) es una resistencia en serie directamente en la salida del oscilador, típicamente en el rango de 22 a 47 Ω. Esta resistencia forma junto con la impedancia de la pista un divisor de tensión que amortigua el flanco y absorbe reflexiones. El valor óptimo resulta de la diferencia entre la impedancia de la pista y la impedancia de salida del driver.

Además, ayudan las pistas cortas con impedancia controlada, la minimización de vías en la línea de reloj, un plano de masa continuo bajo la línea de señal y condensadores de desacoplo suficientes cerca del oscilador (típicamente 100 nF cerámicos más 10 µF). Algunos fabricantes de osciladores CMOS ofrecen además modelos con control de pendiente de flancos (Slew Rate Control) que atenúan el problema ya en el driver.

Para señales diferenciales (LVPECL, LVDS, HCSL), la terminación correcta conforme a la especificación es la medida más importante. Además, las dos líneas de un par diferencial deben conducirse siempre con igual longitud y acoplamiento estrecho para minimizar el skew (diferencias de tiempo de propagación) y mantener el rechazo de modo común.

7. Ayuda para la decisión

La elección del tipo de salida correcto depende esencialmente de cuatro factores: la frecuencia de reloj requerida, la familia lógica del receptor, el presupuesto de potencia disponible y los requisitos de integridad de la señal.

Caso práctico | Recomendación |

| Técnica digital general, µC, FPGA-I/O (hasta ~200 MHz) | CMOS – Solución más sencilla y económica, rail-to-rail, mayor disponibilidad, flexible en la tensión de alimentación (1,8–5,0 V) |

| Sistemas legacy 5V, controles industriales | TTL – Directamente compatible con familias lógicas 5V antiguas; cada vez más sustituido por CMOS con alimentación 5V |

| Aplicaciones RF, circuitos con transformador | Clipped Sine Wave o Sinus – Un menor contenido armónico reduce problemas EMC y permite una síntesis de frecuencia precisa |

| Equipos de red de alta velocidad (>622 MHz) | LVPECL – Máxima velocidad de conmutación, ideal para SONET/SDH, Ethernet PHY y relojes backplane |

| Clocking FPGA, transmisión de datos serie, interfaces de pantalla | LVDS – Compromiso óptimo entre velocidad, consumo y comportamiento EMC |

| Reloj de referencia PCI Express | HCSL – Único estándar de reloj especificado por PCI-SIG para sistemas PCIe |